Fully digital jerk-based chaotic oscillators for high throughput pseudo-random number generators up to 8.77 Gbitss

About

Abhinav S. Mansingka, et al., "Fully digital jerk-based chaotic oscillators for high throughput pseudo-random number generators up to 8.77 Gbitss" Microelectronics Journal 44, (9), 2013, 744.

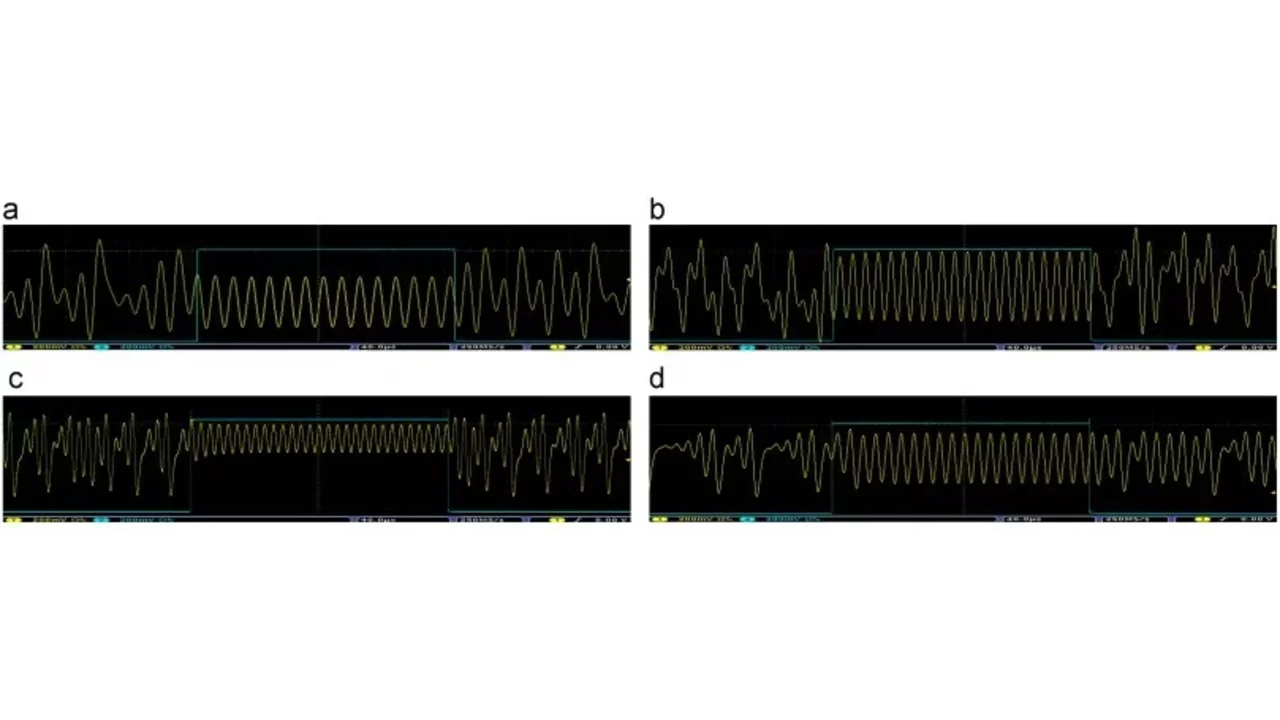

Abstract: This paper introduces fully digital implementations of four different systems in the 3rd order jerk-equation based chaotic family using the Euler approximation. The digitization approach enables controllable chaotic systems that reliably provide sinusoidal or chaotic output based on a selection input. New systems are introduced, derived using logical and arithmetic operations between two system implementations of different bus widths, with up to 100× higher maximum Lyapunov exponent than the original jerk-equation based chaotic systems. The resulting chaotic output is shown to pass the NIST SP. 800-22 statistical test suite for pseudo-random number generators without post-processing by only eliminating the statistically defective bits. The systems are designed in Verilog HDL and experimentally verified on a Xilinx Virtex 4 FPGA for a maximum throughput of 15.59 Gbits/s for the native chaotic output and 8.77 Gbits/s for the resulting pseudo-random number generators.